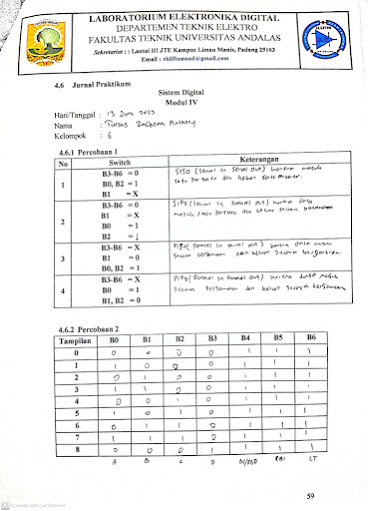

1. Jurnal

[Kembali]

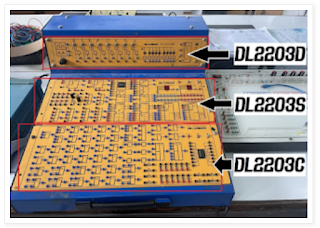

- Panel DL 2203D

- Panel DL 2203S

- Panel DL 2203C

- Jumper

Percobaan 2a

Percobaan 2b

4. Prinsip Kerja Rangkaian

[Kembali]Percobaan 2a.

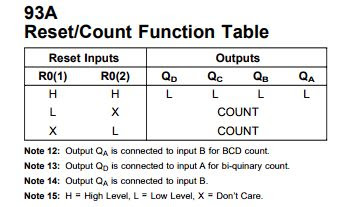

Dalam percobaan ini, kami menggunakan modul D'Lorenzo dengan dua bagian, yaitu DL2203D dan DL2203S. Setiap IC memiliki 6 input dan 4 output. Pada IC 74LS90, B0 dihubungkan ke R0(1) dan B1 dihubungkan ke R0(2). B2 dihubungkan ke R9(1) dan B3 dihubungkan ke R9(2). Indikator untuk mengatur nilai output terletak pada input B0 dan B1. Nilai CKA dihubungkan ke CKB dan dialiri oleh sinyal CLOCK. Sementara pada IC 7493, B4 dihubungkan ke R0(1) dan B5 dihubungkan ke R0(2). Pengaturan nilai output terletak pada B4 dan B5. CKA dihubungkan ke CKB dan dihubungkan paralel dengan CKA dan CKB pada IC 74LS90. Output yang dihasilkan disesuaikan dengan nilai input yang ada dalam modul.

Percobaan 2b.

Pada percobaan ini, hampir mirip dengan percobaan 2a. Perbedaannya terletak pada nilai CLOCK, yaitu CKA dan CKB pada setiap IC. Pada percobaan 2b, output CKA pada IC 7493 dihubungkan paralel dengan CKA pada 74LS90, yang kemudian akan dihubungkan ke sinyal CLOCK. Sementara CKB tidak dihubungkan paralel untuk kedua IC. Nilai CKB pada IC 74LS90 akan menjadi umpan balik untuk nilai output Q0. Hal yang sama juga berlaku untuk IC 7493, dimana nilai CKB menjadi umpan balik untuk nilai output QA. Output yang dihasilkan disesuaikan dengan nilai input yang ada dalam modul.

Percobaan 2a

6. Analisa [Kembali]

1. Analisislah output yang dihasilkan untuk masing-masing IC, baik itu IC 74LS90 maupun IC 7493. Apakah output yang dihasilkan sama? Kalau iya jelaskan kenapa bisa sama dan jika tidak, mengapa bisa berbeda?Jawab:

Output ya berbeda karena IC 7490 memiliki reset setiap output bernilai 9 sehingga maksimum counter tersebut hanya 0-9. sedangkan IC 74LS90 memiliki reset setiap output bernilai 15.

2. Analisalah dan jelaskanlah mengapa pada percobaan 2a kondisi 1, menghasilkan output 0(tidak ada LED yang menyala)? Apa faktor yang mempengaruhinya dan kenapa bisa begitu?

Jawab:

Dikarenakan pada kondisi pertama, nilai input reset bernilai 1 sehingga output pada IC bernilai 1.

3. Pada percobaan 2a dan 2b, terdapat perbedaan pada clocknya. Pada percobaan 2a, clock A dan clock B dihubungkan kesumber clock. Sedangkan pada percobaan 2b, clock A nya dihubungkan kesumber clock, sedangkan clock B dihubungkan ke outputnya H0 dan H4. Apakah hasil yang didapatkan itu sama?Jika iya, kenapa bisa sama dan jika tidak kenapa bisa berbeda, dan dimana letak perbedaannya.

Jawab:

Pada percobaan 2a input clock tidak mendapat feedback sehingga nilai pada counter tidak berurut dari 0-15. pada percobaan 2b input clock mendapat feedback dari output sehingga nilai output counter tidak ada jeda clock dan output akan berurut 0-15.