- Panel DL 2203D

- Panel DL 2203S

- Panel DL 2203C

- Jumper

Dalam eksperimen ini, kami membuat susunan yang sesuai dengan gambar dalam eksperimen 1, yaitu 4 J K Flip Flop dengan 7 sakelar SPDT. Di mana SW 1 terhubung dengan SET pada J K Flip Flop terakhir, SW 2 terhubung dengan SET pada J K Flip Flop ke-3, SW 3 terhubung dengan SET pada J K Flip Flop kedua, dan SW 4 terhubung dengan SET pada J K Flip Flop pertama. SW 5 terhubung ke gerbang AND, SW 6 terhubung ke input J dan K pada Flip Flop pertama, dan SW 7 terhubung dengan RESET pada seluruh Flip Flop.

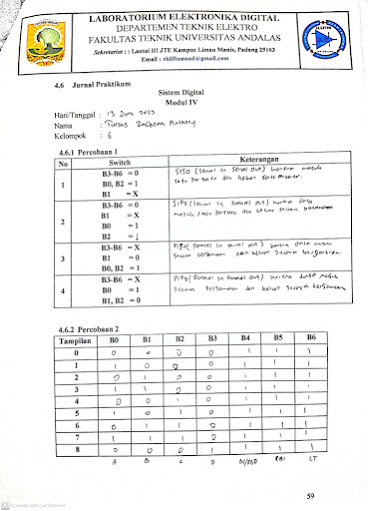

Dalam eksperimen ini, kami memvariasikan nilai-nilai B0-B6. Dari input-input ini, kami mendapatkan hasil sebagai berikut:

- Jika B3-B6=0, B0 dan B2=1, serta B1=X, maka rangkaiannya adalah Serial In Serial Out (SISO).

- Jika B3-B6=0, B0=1, dan B2=Rise Time, serta B1=X, maka rangkaiannya adalah Serial In Parallel Out (SIPO).

- Jika B3-B6=X, B0 dan B2=1, serta B1=0, maka rangkaiannya adalah Parallel In Serial Out (PISO).

- Jika B3-B6=X, B0=1, dan B2=0, serta B1=0, maka rangkaiannya adalah Parallel In Parallel Out (PIPO).

- Kondisi Pertama itu Serial In Serial Out (SISO), karena input data masuk secara berurutan satu persatu dan keluar secara berurutan satu persatu juga.

- Kondisi Kedua itu Serial In Pararel Out (SIPO), karena input data masuk secara berurutan satu persatu dan keluar secara bersamaan.

- Kondisi Ketiga itu Pararel In Serial Out (PISO), karena input data masuk secara bersamaan dan keluar secara berurutan satu persatu.

- Kondisi Keempat itu Pararel In Pararel Out (PIPO), karena input data masuk secara bersamaan dan keluar secara bersamaan.

7. Link Download [Kembali]

No comments:

Post a Comment